Data Flow Modelling in Verilog

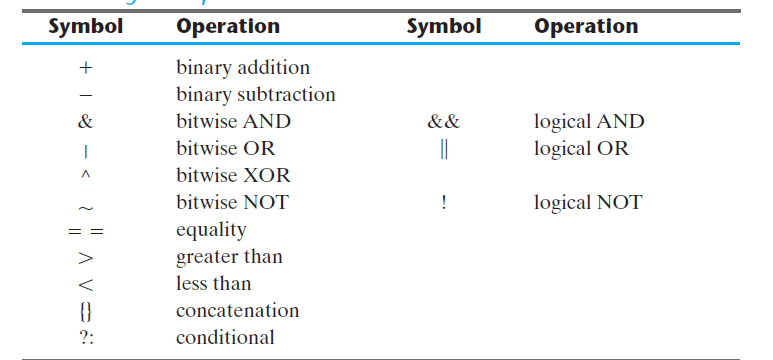

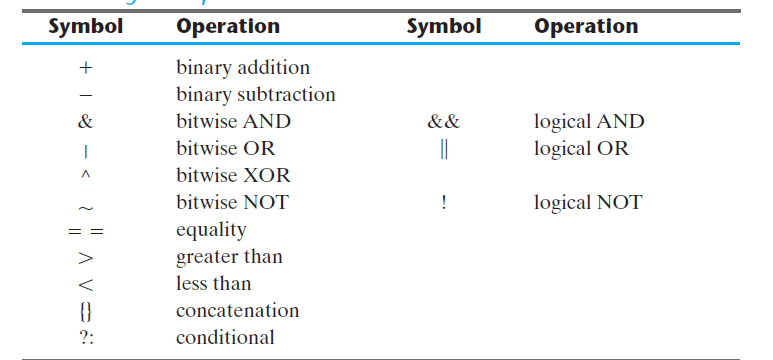

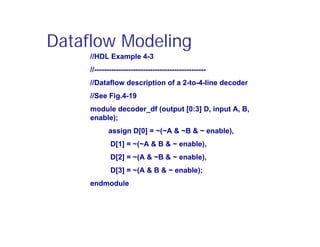

Endmodule Just like the and operation the logical operator performs a binary multiplication of the inputs we write. Then we use assignment statements in data flow modeling.

Data Flow Modeling Verilog Hdl Lecture Slides Slides Verilog And Vhdl Docsity

AEDT provides access to the Ansys gold-standard electromagnetics simulation solutions such as Ansys HFSS Ansys Maxwell Ansys Q3D Extractor Ansys SIwave and Ansys Icepak using electrical CAD ECAD and mechanical CAD MCAD.

. Verilog code for AND gate using data-flow modeling. Switch Level Primitives Switches are unidirectional or bidirectional and resistive or non-resistive for each group those primitives that switch on with a positive gate such as NMOS transistor and those that switch on with a negative gate such as. Ansys Electronics Desktop AEDT The Ansys Electronics Desktop AEDT is a platform that enables true electronics system design.

If you are interested in algorithms performance engineering data capture and analysis trading infrastructure or exchange gateways youll love Akunacademy. Assign Y A. The concurrent statements in VHDL are WHEN and GENERATE.

Verilog Tutorial with What is Verilog Lexical Tokens ASIC Design Flow Chip Abstraction Layers Verilog Data Types Verilog Module RTL Verilog Arrays Port etc. Besides them assignments using only operators AND NOT sll etc can also be used to construct code. Describes how the Vitis development environment lets you build a software application using the OpenCL API to run hardware kernels on accelerator cards like a Xilinx Alveo Data Center accelerator card for FPGA-based acceleration.

Verilog uses a 4 value logic value system so Verilog switch input and output signals can take any of the four 0 1 Z and X logic values. QUANT Quant internships expose you to the financial markets where youll gain experience on anything from identifying and defining significant algorithm improvements our trading strategies pricing models execution logic and. We would again start by declaring the module.

In this modeling style the flow of data through the entity is expressed using concurrent parallel signal. In succession of International Conferences SPIN-2014 SPIN-2015 SPIN-2016 SPIN-2017 SPIN-2018 SPIN-2019 SPIN-2020 SPIN 2021 9th International Conference on Signal Processing and Integrated Networks SPIN-2022 will be organized by Amity University Noida on. Module AND_2_data_flow output Y input A B.

Veriloghdl Basic Data Flow Modelling Youtube

What Is The Difference Between Data Flow And Behavioral Modelling In Verilog Hdl Ee Vibes

Comments

Post a Comment